1

# **Final project**

#### **Due: June 14th**

电子版pdf格式发至邮箱: <u>luojing@sjtu.edu.cn</u> 纸质版上课时交给助教

Presentation at 14:00-15:40, June 14th

### Outline

# 3-bit 50MSPS SAR ADC

- Your task

- 2-stage OPA

Your task

# Choose the one you want to do!

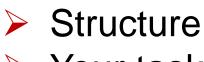

Structure of SAR ADC

Sample and hold, Capacitive DAC, Comparator and SAR logic

4

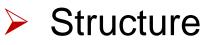

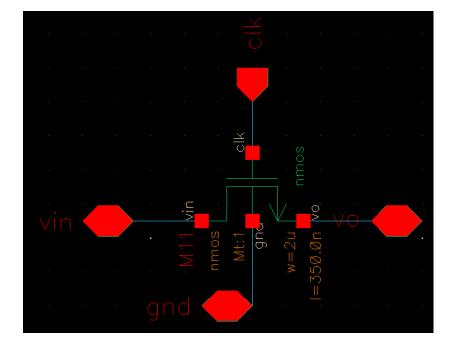

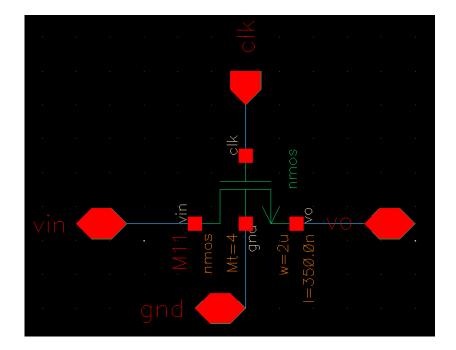

#### Sample and hold — transmission gate

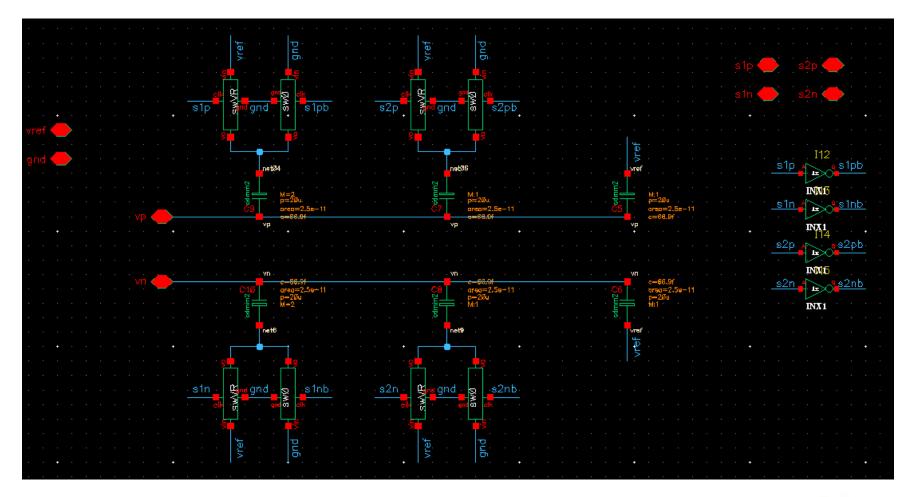

#### ■ Capacitive DAC — unity cap 66.9fF, sw0, swVR

Ynanshai Jiao Tong Universit

sw0,

#### Comparator

と shanghai Jiao Tong University 7

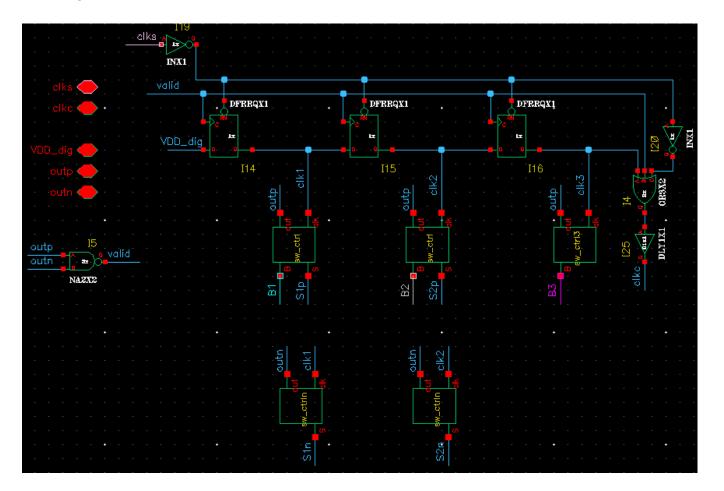

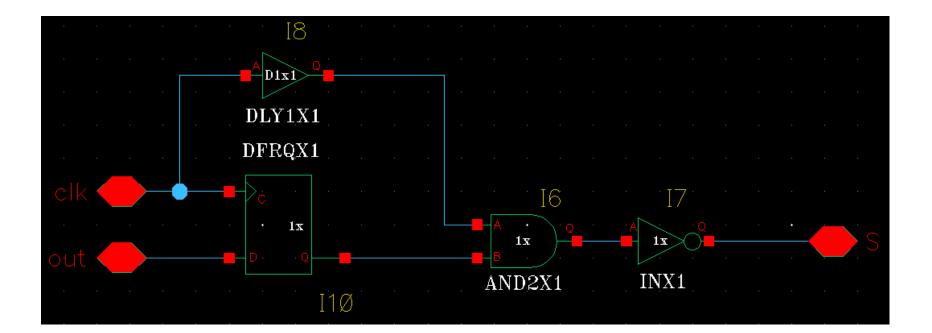

SAR logic — INX, NAND, OR, DFF, sw\_ctrl, sw\_ctrl3, sw\_ctrln

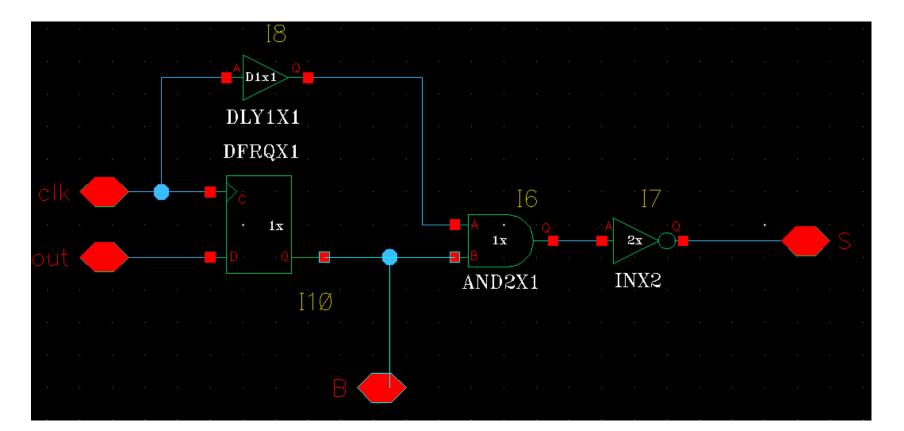

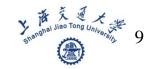

sw\_ctrl

sw\_ctrl3

sw\_ctrln

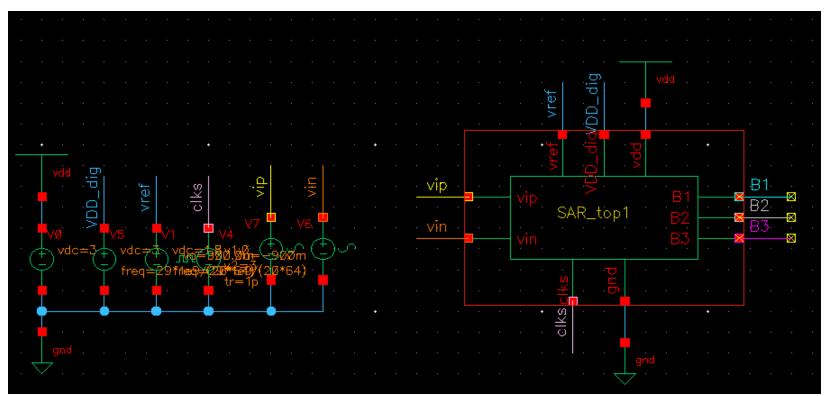

#### Testbench

#### Vdd=3V, VDD\_dig=3V, vref=1.8V

#### Testbench

| Voltage 1   | 0 ¥   |

|-------------|-------|

| Voltage 2   | 3 V   |

| Period      | 20n s |

| Delay time  | 2n s  |

| Rise time   | 1p s  |

| Fall time   | 1p s  |

| Pulse width | 8n s  |

clks

| DC voltage                 | 900.0m V          | DC voltage    |

|----------------------------|-------------------|---------------|

| AC magnitude               |                   | AC magnitud   |

| AC phase                   |                   | AC phase      |

| XF magnitude               |                   | XF magnitud   |

| PAC magnitude              |                   | PAC magnitu   |

| PAC phase                  |                   | PAC phase     |

| Delay time                 | 0 s               | Delay time    |

| Offset voltage             |                   | Offset voltag |

| Amplitude                  | 900.0m V          | Amplitude     |

| Initial phase for Sinusoid |                   | Initial phase |

| Frequency                  | 29*1e9/(20*64) Hz | Frequency     |

vip

| DC voltage                 |  |

|----------------------------|--|

| AC magnitude               |  |

| AC phase                   |  |

| XF magnitude               |  |

| PAC magnitude              |  |

| PAC phase                  |  |

| Delay time                 |  |

| Offset voltage             |  |

| Amplitude                  |  |

| Initial phase for Sinusoid |  |

| Frequency                  |  |

| 900.0m V          |

|-------------------|

| [                 |

|                   |

|                   |

|                   |

| 0 s               |

|                   |

| -900m V           |

|                   |

| 29*1e9/(20*64) Hz |

#### vin

### Your task

- Draw the schematic of SAR ADC

- Do tran pre-simulation and calculate SNDR

- Draw the layout

- Do tran post-simulation and calculate SNDR

- Compare the results and discuss carefully

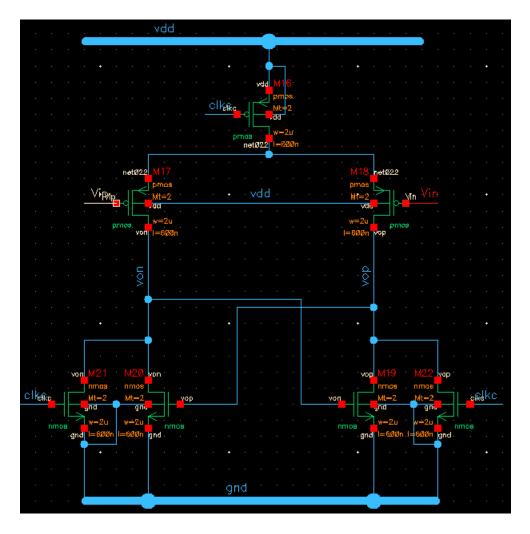

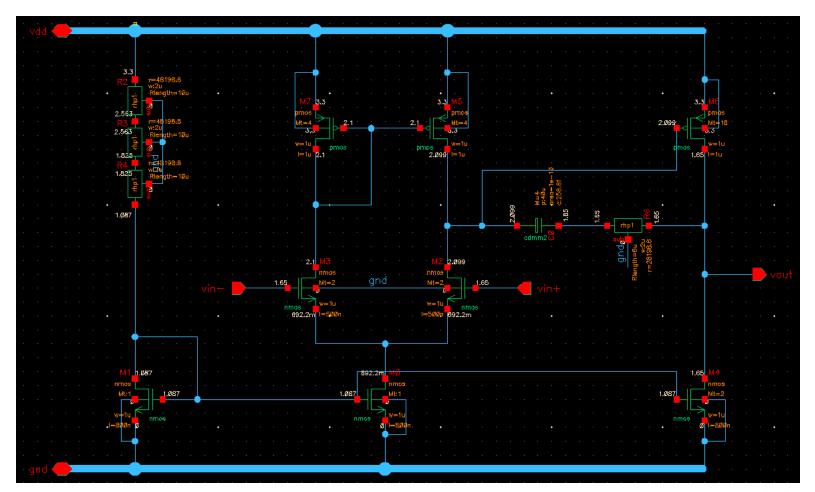

#### Structure of OPA

Shanghai Jiao Tong University 15

#### Structure of OPA

#### Resistor:

| Resistance | 48198.8 Ohms |

|------------|--------------|

| Width      | 2u M         |

| Length     | 10u M        |

| Multiplier | 1            |

#### Rhp1 for bias

| Resistance | 28198.8 Ohms |

|------------|--------------|

| Width      | 2u M         |

| Length     | 6u M         |

| Multiplier | 3            |

#### **Rhp1 for miller compensation**

• Capacitor:

| Unit Capacitance | 258.8f F |  |

|------------------|----------|--|

| Width            | 10u M    |  |

| Length           | 10u M    |  |

| Multiplier       | 4        |  |

| cdmm2            |          |  |

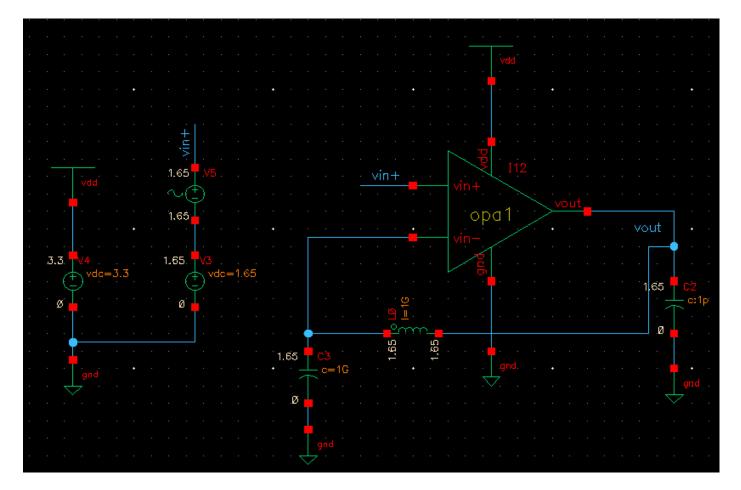

#### Testbench

Shanghai Jiao Tong University 17

### Your task

- Draw the schematic of OPA

- Do pre-simulation and calculate DC gain, PM, GBW (in different PVTs)

- Do monte-carlo pre-simulation

- Draw the layout

- Do post-simulation and calculate DC gain, PM, GBW (in different PVTs)

- Do monte-carlo post-simulation

- Compare the results and discuss carefully

# **Thanks!**

IS